DDR-SDRAM……勉強ついでにSRAM、DDR-SDRAMの解説

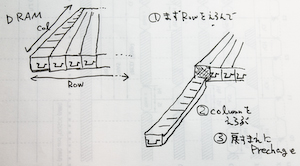

データシートを電車の中で読み続けてなんとか概略は掴んだので、ちょいと現実逃避で解説。解説といっても現実的な解説じゃなくて、データアクセス方法的な解説だけども。DRAMにもいろいろあるのかもしれないけども。とりあえずDDR-SDRAMのデータシートからのイメージ。

SRAM

まず、比較の為にSRAMから。

引き出しの中にデータ(ビット)が入っているとすると、横に引き出しが並んでいるイメージ。

全部に取っ手がついているので、何番地と言えばすぐにデータがでてくる。単純。

DDR-SDRAM

DRAMは、奥に長い引き出しが並んでいるイメージ。引き出しは長いだけあってたくさんデータが入っている。

データを読んだり書いたりするには、なにはともあれ、まず引き出しをひっぱりだしてこなきゃいけない。そのあとようやくアクセスできるようになる。で、アクセスがおわったらちゃんと引き出しを締めなきゃいけない(プリチャージ)。けっこうこの出し入れに時間がかかる。しかも、奥に長い引き出しなので通気性が悪く腐っちゃうので、定期的に掃除しなきゃいけない(リフレッシュ)。

DDR-SDRAMは、このDRAMの構造の上に、クロックの立ち上がり、立ち下がり両方でのデータ送受信可能な仕組みを作って性能を向上させている。

このかったるい仕組みに速さを両立させるために、バースト(連続番地)読み出しとか、書き込みとか、バンク(このタンスがまた別にあるイメージ。あるタンスの引き出しをずりずり出している間に別のタンスのデータを読んだりできる)とか、涙ぐましい努力がされている。で、扱いにくくなっているという。

ちょっとおもしろかったのが、auto refresh関連の以下のくだり

During auto refresh, the addressing is generated by the internal refresh controller. Thismakes the address bits a “Don’t Care” during an AUTO REFRESH command. The DDR SDRAM requires AUTO REFRESH cycles at an average interval of tREFI (MAX).

To allow for improved efficiency in scheduling and switching between tasks, some flexibility in the absolute refresh interval is provided. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM, meaning that the maximum absolute interval between any AUTO REFRESH command and the next AUTO REFRESH command is 9 x tREFI(= tREFC). JEDEC specifications only allow 8 x tREFI; Micron specifications

exceed the JEDEC requirement by one clock.

(読み違えてなければ)ひまなときにたくさんrefreshコマンドを発行できるそうな。まじですか。5回やったら5回分さぼっていいという。最初にたくさん寝とけば4徹5徹ができるみたいな(笑)。

しかしまあ、こんなのよく流行るよなぁ……とおもうけど、容量の面でいったらDRAMのほうが圧倒的に安いわけで、しょうがないといえばしょうがない。

ちゃんとFPGAに実装できるかどうか自信ないわ。。